- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA644P-B15MZ (Atmel)IC MCU 8BIT 64KB FLASH 32VQFN

46

7674F–AVR–09/09

ATmega164P/324P/644P

8.12

Register Description

8.12.1

SMCR – Sleep Mode Control Register

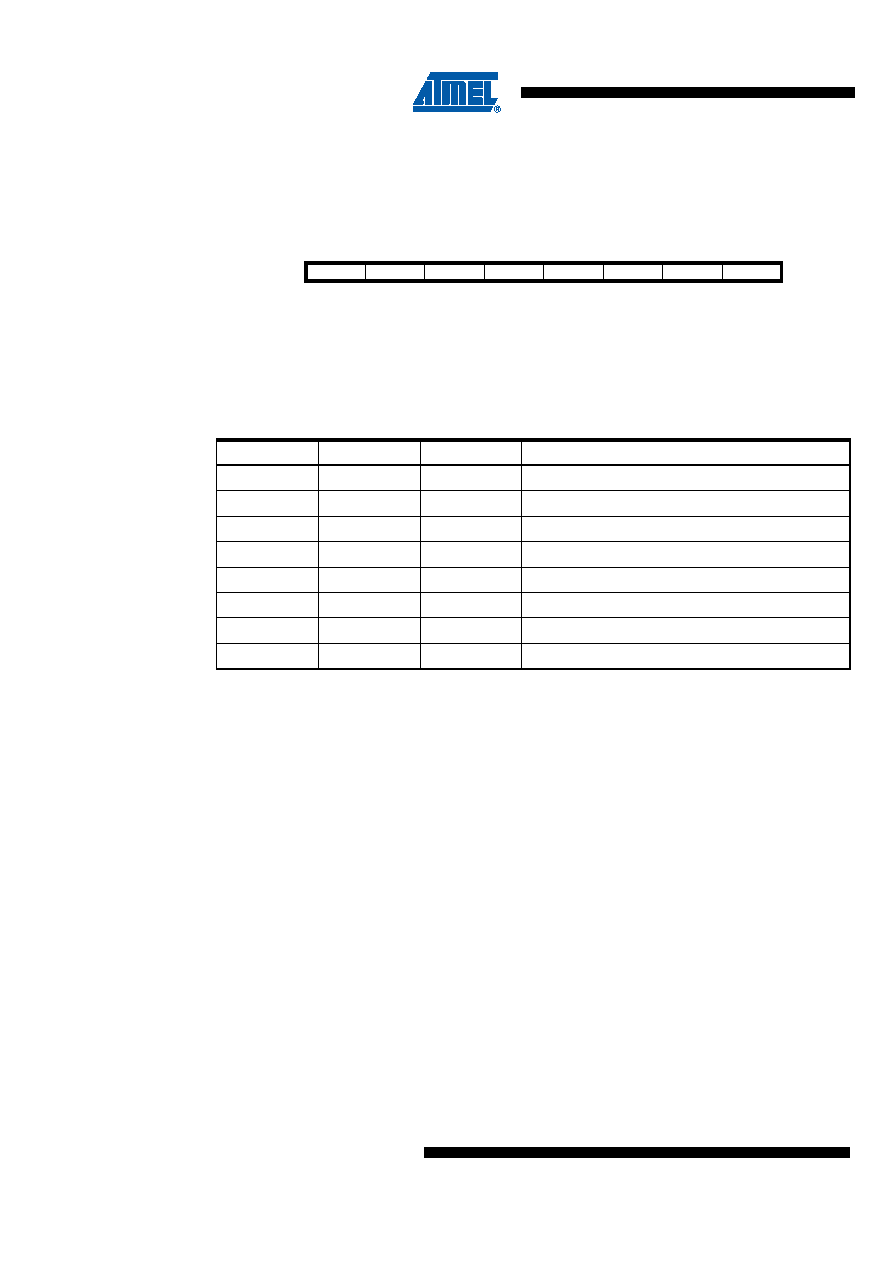

The Sleep Mode Control Register contains control bits for power management.

Bits 3, 2, 1 – SM2:0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the five available sleep modes as shown in Table 8-2.

Note:

1. Standby modes are only recommended for use with external crystals or resonators.

Bit 0 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP

instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmer’s

purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of

the SLEEP instruction and to clear it immediately after waking up.

Bit

7

6

543210

––

SM2

SM1

SM0

SE

SMCR

Read/Write

RRRR

R/W

Initial Value

0

000000

Table 8-2.

Sleep Mode Select

SM2

SM1

SM0

Sleep Mode

000

Idle

0

1

ADC Noise Reduction

010

Power-down

011

Power-save

100

Reserved

101

Reserved

110

Standby(1)

1

Extended Standby(1)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATMEGA644V-10PU

IC AVR MCU FLASH 64K 40DIP

ATMEGA645V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA649-16MI

IC AVR MCU FLASH 64K 5V 64QFN

ATMEGA649V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA8515L-8JUR

MCU AVR 8KB FLASH 8MHZ 44PLCC

ATMEGA8515L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

ATMEGA8535-16JUR

MCU AVR 8K FLASH 16MHZ 44PLCC

ATMEGA8535L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

相关代理商/技术参数

ATMEGA644PR212-AU

功能描述:8位微控制器 -MCU ATmega 644PV-10AU AT86RF212-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR212-MU

功能描述:8位微控制器 -MCU ATmega 644PV-10MU AT86RF212-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR231-AU

功能描述:8位微控制器 -MCU ATmega 644PV-10AU AT86RF231-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR231-MU

功能描述:8位微控制器 -MCU ATmega 644PV-10MU AT86RF231-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AQ

功能描述:8位微控制器 -MCU AVR 64KB, 2KB EE 20MHz 4KB SRAM, 1.8V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AQR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM-20MHz, 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AU

功能描述:8位微控制器 -MCU AVR 64K FLASH 2K EE 4K SRAM ADC-10MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AUR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM-10MHz, 1.8V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT